# Использование комплекта разработки NT102-0272 XtremeDSP для решения задачи демультиплексирования цифровых сигналов с помощью ПЛИС

#### Павел Львов, Александр Тумачек (Московская обл.)

В статье рассмотрены особенности функционирования основных аппаратных блоков цифрового демультиплексора, построенного на базе комплекта NT102-0272 XtremeDSP. Даны рекомендации по их применению.

При решении задачи демультиплексирования цифрового потока с помощью ПЛИС большое внимание должно уделяться не только скоростным показателям ПЛИС, но и периферийным устройствам, поскольку важна временная привязка устройства к потоку. Рассмотрим основные аппаратные блоки демультиплексора.

## ПЛИС семейства Virtex-4 (4vsx35ff668)

При демультиплексировании наиболее ресурсоёмкими являются структурные блоки разуплотнения цифрового потока на подканалы. Степень иерархии в геометрической прогрессии влияет на количество используемых логических элементов [1–4]. На основе ПЛИС Virtex-4 возможно реализовать потоковый демультиплексор сигналов E2 – E3.

Необходимо отметить наиболее важные свойства выбранной ПЛИС (см. таблицу 1) для решения задачи демультиплексирования.

Технология синхронизации Xesium [5] обеспечивает:

- точную подстройку фазы тактовых сигналов;

- умножение и деление частоты;

- низкое энергопотребление;

- дополнительный фазированный делитель тактового сигнала (РМСD);

- дифференциальную структуру синхронизации для минимизации фазовых дрожаний тактовых сигналов и обеспечения скважности 50%;

- 32 цепи глобальных тактовых сиг-

- Модуль XtremeDSP [5] реализует:

- умножитель 18 × 18, умножитель-накопитель, умножитель-сумматор;

- возможность организации конвейерной обработки данных для увеличения производительности плис.

- встроенный 48-битный блок для выполнения операции умножения с накоплением (MACC);

- интегрированный сумматор (выполнен на кристалле как отдельный элемент) для выполнения операций умножения с суммированием;

- возможность каскадирования умножителей или МАСС;

- иерархию памяти ОЗУ;

- двухпортовую архитектуру памяти ОЗУ;

- возможность запрограммировать ОЗУ как очередь FIFO, поддерживающую флаги «пустой», «полный», программируемые флаги «почти полный» и «почти пустой» и возможный» и «почти пустой» и возможный»

- ность работы в синхронном и асинхронном режимах;

- независимый выбор разрядности порта чтения и записи (в конфигурации ОЗУ);

- конфигурации блоков ОЗУ от 16К×1 до 512К×36 (от 4К×4 до 512К×36 в режиме FIFO).

Технология SelectIO [5] обеспечивает производительность до 600 Мбит/с HSTL (High Speed Transceiver Logic) при передаче по одному выводу входа/выхода и до 1 Гбит/с при передаче по дифференциальной паре ввода-вывола LVDS.

#### Интерфейс РСІ

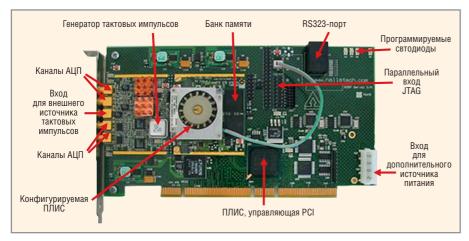

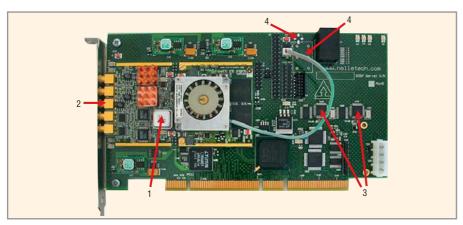

Для управления устройством ввода-вывода на базе шинного интерфейса РСІ применяется контроллер, реализующий протокол передачи данных. Таким контроллером на платформе NT102-0272 XtremeDSP от Nallatech (см. рис. 1) является ПЛИС семейства Spartan 2 от Xilinx, которая сконфигурирована для выполнения функций контроллера РСІ и не предназначена для перепроектирования. Связь между контроллером и проектируемой ПЛИС осуществляется с помощью шины данных (разрядность 32 бита, работа на частоте до 33 МГц) и шины управления (разрядность 7 бит).

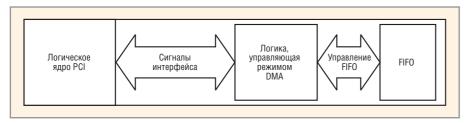

Для реализации протоколов передачи данных, ПЛИС, управляющая шиной РСІ, конфигурируется производителем соответствующим модулем. Применительно к анализируемой платформе этот модуль называется ядром интерфейса РСІ (РСІ communications core). Рассмотрим режим прямого доступа к памяти (DMA, ПДП), блок-схема которого приведена на рисунке 2.

Режим ПДП предназначен для передачи больших объёмов данных через интерфейс РСІ. Контроллер реализует протокол передачи через контейнер FIFO с помощью двух регистров, что необходимо для общего управления

Таблица 1. Основные технические характеристики ПЛИС Virtex-4 (4vsx35ff668)

| Матрица конфигурируемого логического блока                           | 96 × 40 |

|----------------------------------------------------------------------|---------|

| Логические ячейки                                                    | 34 560  |

| Распределённое ОЗУ, Кбит                                             | 240     |

| Блочное ОЗУ, Кбит                                                    | 3456    |

| Модули ЦПОС (DSP)                                                    | 192     |

| Модули DCM (цифровой блок управления синхронизацией)                 | 8       |

| Модули PMCD (дополнительный фазированный делитель тактового сигнала) | 4       |

| Число пользовательских контактов                                     | 448     |

Рис. 1. Внешний вид платы из комплекта разработки NT102-0272 XtremeDSP

Рис. 2. Блок-схема реализации ПДП

двумя режимами, но такое решение даёт значительное улучшение скоростных показателей передачи. Ускорение обусловлено увеличением количества переданных слов за единицу времени по сравнению с другими режимами.

Для управления в режиме ПДП используются два внутренних регистра контроля состояния и регистр счётчика. Регистр счётчика хранит количество слов, которые ожидают передачи. Он должен быть установлен до инициализации режима. Счётчик считает в обратном направлении при чтении или записи. Когда он достигает нуля, передача прекращается. Одновременно реализуется до 16 каналов передачи, их количество также программируется заранее.

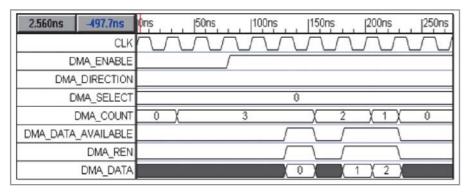

При записи данных в приложение пользователя реализация режима ПДП является сравнительно простой (см.

рис. 3). Первоначально должен быть установлен счётчик. После этого инициализируется режим прямого доступа (сигнал DMA\_Enable устанавливается в лог. 1) и начинается передача. Сигнал DMA\_DATA\_AVAILABLE, установленный в лог. 1, гарантирует, что запись началась.

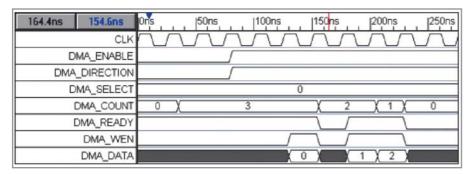

При чтении данных из приложения пользователя также первоначально устанавливается счётчик, но инициализация режима происходит несколько иначе (см. рис. 4). Сигнал DMA\_DI-RECTION олжен быть установлен в лог. 1 вместе с сигналом DMA\_ENABLE. В данном случае контроль выполняет сигнал DMA\_RDY — при лог. 1 шина данных готова к чтению.

#### Интерфейс RS-232

Для сопряжения с другими аппаратными средствами фирма Nallatech

Таблица 2. Описание имеющихся разъёмов порта RS-232

| Разъём | Номер контакта | Функции контакта | Изображение |

|--------|----------------|------------------|-------------|

| J9     | 1              | Передача         | 3 4         |

|        | 2              | Приём            |             |

|        | 3              | Земля            |             |

|        | 4              | Земля            |             |

| J12    | 1              | Нет подключения  | 1 6         |

|        | 2              | Земля            |             |

|        | 3              | Передача         |             |

|        | 4              | Приём            |             |

|        | 5              | Земля            | W (1 W)     |

|        | 6              | Нет подключения  |             |

Рис. 3. Временная диаграмма записи данных в режиме ПДП

Рис. 4. Временная диаграмма чтения данных в режиме ПДП

Рис. 5. Расположение источников синхронизирующего сигнала на плате

Рис. 6. Расположение розетки для подключения внешних генераторов синхронизирующих сигналов на плате

снабдила рассматриваемый комплект цифровым портом ввода-вывода, реализующим протокол передачи данных RS-232 (интерфейс между терминальным оборудованием и связным оборудованием с обменом по последовательному двоичному коду). Интерфейс реализован на микросхеме MAX4144, обеспечивающей высокоскоростную работу и использующей архитектуру на трёх операционных усилителях.

Платформа предоставляет разработчику два порта, предназначенных для реализации протокола RS-232. В таблице 2 приведено соотношение сигналов и контактов на изображениях.

#### Таймеры синхронизации

Плата предоставляет гибкую систему таймеров синхронизации, обеспечивающих правильную работу цифро-

вых компонентов. Существует несколько различных источников тактовых импульсов (см. рис. 5):

- кварцевый автогенератор 105 МГц);

- разъём для подключения внешнего устройства синхронизации;

- два программируемых источника, которые могут быть настроены на различные частоты по желанию разработчика проекта;

- розетка для подключения специальных генераторов (см. рис. 6).

Всеми источниками синхронизации управляет отдельная конфигурируемая ПЛИС семейства Virtex-2 серии хс2v80. Для её настройки разработчик создаёт специфический проект синхронизирующего устройства и конфигурирует ПЛИС с помощью загрузочного кабеля через порт JTAG, аналогично основной ПЛИС.

#### Заключение

В статье рассмотрены особенности реализации модулей комплекта разработки NT102-0272 XtremeDSP фирмы Nallatech. Показано, что на основе этих инструментальных средств возможна разработка сложного устройства цифровой обработки сигналов. Отмечено, что наиболее трудоёмким процессом разработки является настройка протокола передачи данных по внешним шинам (PCI, RS-232) как со стороны ПЛИС (управление контроллером), так и со стороны управляющего устройства (работа с драйвером). Таким образом, для успешного проектирования устройства ЦОС необходимо изучить не только программные средства проектирования и архитектуру выбранной ПЛИС, но и принципы работы периферийных модулей (передачу данных, синхронизацию и т.д.).

#### Литература

- Лобов В.И. Теоретические основы цифровой обработки сигналов. Москва, 2008.

- Максфилд К. Проектирование на ПЛИС. Додэка-XXI, 2007.

- Крушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П.

Проектирование систем на микросхемах

с программируемой структурой. БХВ Петербург, 2006.

- Зотов В.Ю. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE. Горячая линия – Телеком, 2003.

- 5. www.xilinx.com.

### Новости мира News of the World Новости мира

#### Канун SDR-революции

Одной из прорывных технологий для систем беспроводной связи может стать «программное радио» (Software Defined Radio, SDR).

Суть концепции SDR проста и элегантна: создать компактное устройство, в котором функциональные возможности специализированной элементной базы (отдельные микросхемы для поддержки технологий GSM, GPS, Bluetooth, Wi-Fi и т.д.), применяемой для обработки радиосигналов в коммуникационных каналах на основе разных технологий, заменяется работой одного процессора, проводящего те же операции «расшифровки» схем модуляции и кодирования исключительно программными методами.

Смартфон на основе технологии «программного радио» был бы не только легче, меньше и (возможно) дешевле нынешних, но и более энергоэффективным. Он обладал бы «интеллектом», обеспечивающим владельца смартфона оптимальным доступом к каналу связи: «умный» SDR-аппарат был бы способен автоматически отыскивать самый лучший и наименее дорогостоящий способ соединения с нужным абонентом.

SDR-технология упрощает жизнь и производителям коммуникационного оборудования. При появлении нового стандарта радиокоммуникаций им пришлось бы дополнить (изменить) лишь программное обеспечение (ПО), не затрагивая аппаратной платформы. А проблема исправления технических глюков решалась бы тривиальным скачиванием очередного патча.

Что же касается провайдеров беспроводной связи, то они получили бы небывалые возможности для оперативного и технологичного (без модификации «железа») разворачивания всевозможных новых сервисов

Хотя на сегодняшний день надлежащий технический уровень для повсеместного распространения SDR не достигнут, по мнению ряда специалистов, эпоха «программного радио» уже не за горами. И в этом — немалая заслуга разработчиков на базе технологий Open Source.

Около десятилетия тому назад некоторые из любителей-энтузиастов «программного радио» заинтересовались дебатами, которые шли в ту пору во властных структурах Вашингтона вокруг технологии broadcast flag. С её помощью Голливуд хотел принудительно заставить телевизионное оборудование заниматься выявлением в эфирных передачах особых метаданных,

которые бытовые ТВ-приёмники должны были воспринимать как команды для безусловного выполнения, жёстко диктующие то, что разрешено и что запрещено делать с принимаемым из эфира телевизионным контентом.

Эрик Блоссом (Eric Blossom), основатель открытого проекта под названием GNU Radio, решил, что создание им ресивера HDTV в программном виде и сопутствующая публикация его в виде открытых исходных кодов должны наглядно продемонстрировать бесперспективность запретительных подходов к проблеме контроля за контентом. Ведь будет достаточно совсем немного поколдовать с кодом программы, чтобы отключить обработку запретительного сигнала, а затем перекомпилировать программу обработки сигнала.

Эта разработка привела к появлению масштабных проектов, ориентированных на более широкий спектр аппаратного обеспечения, на значительно более широкий диапазон частот, на способность к работе сразу с несколькими разными антеннами одновременно.

На базе GNU Radio за прошедшее десятилетие удалось создать немало SDR-изделий, нацеленных на удешевление и общедоступность перспективной технологии. Однако действительно регулярно, примерно раз в квартал, такого рода новости стали приходить лишь в 2012 г.

Минувшей весной один радиолюбитель обнаружил (и рассказал общественности на reddit.com), что 20-долларовый DVBтюнер с цифровой частью Realtek и аналоговой от Elonics E4000 - это уже практически готовый SDR-аппарат. И с помощью одной незадокументированной изготовителем инструкции, ноутбука и ПО GNU Radio этот USB-модуль можно превращать в комплекс SDR с диапазоном рабочих радиочастот от полусотни мегагерц до почти двух гигагерц. (Такие штуки мгновенно раскупили энтузиасты со всего мира, и нынче такой USB-брелок с нужной связкой чипов стоит уже совсем других денег. – Прим. ред.)

К лету 2012 г. на рынке появился SDRпродукт куда более серьёзного уровня – компьютерная плата расширения Phi от небольшой американской фирмы Per Vices. Цена этой платы – порядка 750 долл.

К осени 2012 г. стало известно, что уже почти готов и скоро появится в продаже SDR-аппарат HackRF от компании Great Scott Gadgets, реализованный в виде внешнего USB-устройства размером с портативный жёсткий диск. Рабочий диапазон

частот этого устройства – от 100 МГц до 6 ГГц, цена – порядка 300 долл.

В проекте HackRF наиболее любопытным представляется то, что эту разработку на основе GNU Radio в её финальной фазе профинансировало DARPA — Агентство перспективных военных исследований США, выделив 200 000 долл.

http://www.3dnews.ru/

# IBM и «Ангстрем» подписали стратегические соглашения для развития технологических инноваций

Корпорация IBM, НПО «Ангстрем» и «Ангстрем-Т» подписали коммерческое соглашение и меморандум о взаимопонимании в вопросах сотрудничества по развитию технологических инноваций.

Согласно первому соглашению, ІВМ лицензирует «Ангстрему» технологию производства интегральных схем с топологическими нормами 90 нм. Используя эту технологию, «Ангстрем» планирует запустить производство микроэлектронных устройств, таких как микрочипы и датчики, для продвижения в индустриальном и потребительском сегментах. Помимо лицензии на использование технологии, «Ангстрем» получит от IBM правила проектирования, необходимые для организации контрактного производства, и сможет предложить услуги Smart Foundry российским и зарубежным заказчикам

Финансирование приобретения и установки технологии на строящемся в Зеленограде микроэлектронном заводе «Ангстрем-Т» осуществляет Государственная корпорация «Банк развития и внешнеэкономической деятельности (Внешэкономбанк)».

В свою очередь, меморандум о взаимопонимании определяет формат сотрудничества в сфере исследований и разработок с использованием инновационных технологий.

В соответствии с подписанным Меморандумом, стороны намерены изучать взаимовыгодные модели и возможности потенциального сотрудничества на новых рынках, требующих передовых технологических инноваций и разработок. Потенциальное сотрудничество включает в себя такие сферы, как химия, электротехника, информатика, материаловедение, математика, физика и микроэлектроника.

http://www-03.ibm.com/press/ru/ru/ pressrelease/39286.wss