# СБИС с программируемой архитектурой в системах специального назначения

Часть 1

## Александр Бутов (Москва)

Статья посвящена анализу особенностей применения СБИС с программируемой архитектурой в специализированных системах. В статье рассмотрены существующие архитектуры программируемых СБИС, таких как ПЛИС, программируемые системы на кристалле (ПСНК), структурированные БМК (СБМК). Проведён анализ подходов при разработке современной, сложной аппаратуры, требующей применения оригинальных СБИС. В статье показано, что реализация логики на базе функциональных генераторов (LUT) позволяет существенно упростить и удешевить проектирование схем, изготавливаемых по технологиям с нанометровыми проектными нормами. Предложена методология, позволяющая организовать в России выпуск высокономенклатурных, мелкосерийных СБИС с приёмкой «5».

#### Введение

Разработка современных систем вооружений, средств спецсвязи, бортовой электроники требует применения всё более сложной элементной базы с характеристиками, определяемыми передовым уровнем современной технологии. Разработка такой элементной базы (СБИС и систем на кристалле) является очень сложной интеллектуальной задачей. Для её решения в настоящее время предлагается достаточно мощный пакет средств проектирования, включая разработку проектов на поведенческих языках (Систем C, Verilog HDL), а также развитые средства моделирования и верификации проектов [1-5]. Тем не менее, вероятность получения с первой итерации полностью работоспособных образцов СБИС и особенно СНК является достаточно низкой, что объясняется следующими причинами:

- трудность составления исчерпывающего технического задания для сложных систем;

- наличие труднопрогнозируемых факторов, которые проявляются только при проведении реальных испытаний аппаратуры;

- высокая комбинаторная сложность решаемых задач и, как следствие, наличие риска появления ошибок, объясняемых человеческим фактором.

Обнаружение ошибок и нестыковок в проектах типа ASIC неизбежно приводит к необходимости коррекции, что выливается в существенные временные и финансовые потери. Отметим, что применение в серийной спецаппаратуре СБИС типа ASIC требует проведения длительных (до 1 года) и

дорогостоящих квалификационных испытаний.

По этой причине в настоящее время стали всё шире применяться технологии проектирования, позволяющие выполнять параллельную отработку элементной базы и аппаратуры.

Одним из популярных вариантов такой технологии проектирования является применение СБИС с программируемой архитектурой, позволяющих существенно снизить временные и финансовые затраты на повторные коррекции и изготовление микросхем. Рассмотрим основные типы этих схем.

## ПЛИС И ПРОГРАММИРУЕМЫЕ СИСТЕМЫ НА КРИСТАЛЛЕ

ПЛИС и программируемые системы на кристалле (ПСНК) являются, пожалуй, наиболее удобной элементной базой для разработчиков аппаратуры. Они настраиваются на требуемую конфигурацию программным путём. Микросхемы этого типа хорошо известны нашим разработчикам. В качестве примера можно привести ПЛИС фирм Xilinx, Altera и Actel [6–8].

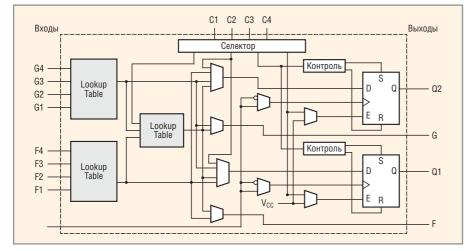

Основу современных ПЛИС составляют логические элементы, позволяющие настраиваться на выполнение логических функций с помощью записи информации, содержащей таблицы истинности функций, в блоки Look-Up Table (поисковая таблица) и информации о структуре связей элемента в память программируемых мультиплексоров. Для создания необходимых связей в ПЛИС применяются программируемые коммутаторы. Пример структуры логического элемента ПЛИС типа FPGA приведён на рис. 1.

Для хранения программируемой информации обычно используется статическая память (RAM), хотя иногда применяется метод занесения информации путём электрического пережигания/восстановления плавких перемычек.

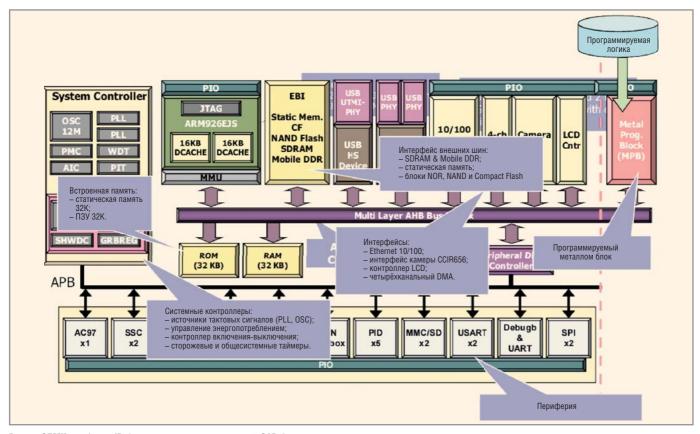

ПЛИС обычно включают в свой состав программируемые цифровые вентили, блоки синхронизации и блоки памяти. ПСНК могут включать в свой состав дополнительный набор IP-бло-

Рис. 1. Структура элемента FPGA

ков, таких как процессорные ядра, интерфейсные блоки, блоки специальной цифровой обработки и даже цифроаналоговые блоки.

ПСНК являются полностью программируемыми системами. В ПЗУ записывается программное обеспечение процессора, в массив FPGA помещается вся специализированная цифровая логика, системный программируемый коммутатор позволяет в широких пределах настраивать систему соединений блоков, в том числе подключение необходимых интерфейсов, вывод на контактные площадки требуемых входных и выходных сигналов, а также настройку аналоговых блоков.

С помощью ПЛИС и ПСНК можно достаточно быстро, с минимальными затратами выполнить разработку и отладку в аппаратуре проекта СБИС, однако при этом технические характеристики и стоимость образцов СБИС существенно уступают специализированным схемам. Поэтому при переходе к серийному производству ответственных изделий неизбежно встаёт вопрос о переводе проектов на более компактную и надёжную элементную базу.

#### Классические БМК

Одним из ранних известных подходов, позволяющих существенно сократить и упростить изготовление БИС, является проектирование и изготовление БИС на базе классических базовых матричных кристаллов (БМК).

Основная идея БМК заключается в создании специальных базовых крис-

таллов – заготовок, содержащих нескоммутированные логические элементы. Эти элементы с помощью нескольких переменных слоёв верхней металлизации настраиваются на выполнение требуемой поведенческой функции. В этих же слоях осуществляется прокладка цепей коммутации.

По своей сути классические БМК, или Gate Array, – это изделия-полуфабрикаты, позволяющие за счёт большого объёма предварительно проведённых работ резко сократить сроки и стоимость разработки специализированных СБИС.

При разработке БМК создаются:

- библиотека стандартных элементов;

- конструкторская и технологическая документация;

- измерительная и испытательная оснастка;

- TY:

- технология и маршрут проектирования

По окончании выполнения ОКР по разработке БМК проектируется тестовая зашивка, на которой проводятся испытания согласно ГОСТ.

Проведение такого большого объёма предварительных работ даёт возможность за 2–4 месяца разрабатывать и выпускать схемы, удовлетворяющие требованиям военной приёмки без проведения длительных квалификационных испытаний и выпуска технической документации. По этой причине при разработке аппаратуры специального назначения разработчики всю её нестандартную часть очень часто выполняют исключительно на БМК,

поскольку разработка специализированных БИС (ASIC) с проведением испытаний и выпуском документации занимает 2–3 года.

Современные технологии проектирования зашивок на БМК или полузаказных БИС позволяют принимать проекты, подготовленные на различных уровнях представления: поведенческие, структурные, представленные в базисе ПЛИС и т.д. Всё это существенно снижает квалификационные требования к специалистам – разработчикам аппаратуры, освобождает их от анализа тонкостей проектирования БИС и фактически переводит разработку изделий в плоскость печатных плат.

В последнее время при проектировании изделий специального применения стала внедряться технология разработки аппаратуры, при которой экспериментальные образцы специализированных БИС разрабатываются на базе импортных ПЛИС, а затем эти проекты при переходе к серийному производству перерабатываются (конвертируются) в отечественные на радиационно-стойкие БМК [11–13].

Задача такой конвертации, на первый взгляд, кажется не очень сложной, однако при ближайшем рассмотрении обнаруживается ряд существенных проблем, обусловленных:

- различным конструктивным исполнением ПЛИС и БМК;

- различными библиотеками;

- различными динамическими параметрами (которые могут отличаться в 5...10 раз);

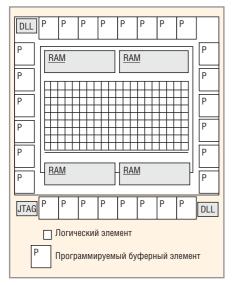

Рис. 2. Структурированный БМК

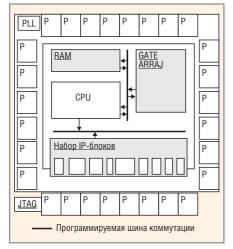

Рис. 3. Структурированный БМК с IP-блоками (гибридная система)

- наличием в ПЛИС большого объёма интеллектуальной аппаратуры, не входящей явно в описание схем (схемы синхронизации, сброса, JTAG и т.д.);

- нестыковкой по документации (БМК требуют наличия полного тестового вектора для измерений, ПЛИС зачастую отлаживают непосредственно в аппаратуре).

Вышеперечисленные проблемы обуславливают относительно большой объём работ по конвертации проектов, который в общем случае не намного быстрее и дешевле оригинальной разработки полузаказной БИС.

#### Структурированные БМК

Структурированные БМК (СБМК) — новый класс БИС, который занимает место между сложными ПЛИС (FPGA) и специализированными БИС (ASIC). В последние годы он завоёвывает всё большую популярность. Производители СБМК стремятся соединить в них

простую и недорогую разработку проектов, свойственную FPGA, с экономным расходом площади и высоким быстродействием ASIC [21].

В отличие от классических БМК, собираемых из мелкозернистых ячеек типа вентиля 2И-НЕ, СБМК строятся на базе крупнозернистых логических блоков, позволяющих реализовывать более сложные функции типа одноразрядного сумматора или ЈК-триггера. Такой подход существенно упрощает выполнение настройки и коммутации логических блоков, сокращает число переменных фотошаблонов и обеспечивает высокие параметры быстродействия, хотя и снижает эффективность использования кремния.

Полузаказные БИС на базе структурированных БМК в настоящее время поставляют фирмы: Chip Express (СХ4000, СХ5000) [7], eASIC (eASIC Array) [8], Faraday Technology (3MPCA), LSI Logic (RapidChip), AMI Semiconductor (Xpress Arrays) и др.

СБМК содержат в своём составе настраиваемые узлы и логические блоки, функции и связи которых программируются масочно. Цифровые вентили СБМК обычно выполняются по идеологии ПЛИС (FPGA или FLEX) с той лишь разницей, что они программируются не путём записи информации в конфигурационной ОЗУ, а с помощью системы переменных перемычек или переменных контактов, выполняемых в одном или двух переменных слоях с помощью фотолитографии или лазерной литографии верхнего слоя металлизации или слоя контактных

Отдельные продвинутые разработки фирм Chip Express и eASIC позволяют это делать даже с помощью одного переменного шаблона. Резкое сокращение числа шаблонов позволяет существенно удешевить и ускорить процесс изготовления микросхем, доведя его до 7–10 дней.

СБМК, кроме программируемых переменными шаблонами цифровых вентилей, могут включать в свой состав дополнительную аппаратуру: процессорные ядра, блоки ЦОС, ОЗУ, ПЗУ, универсальные и специальные блоки ввода-вывода, аналоговые компоненты. Совокупность встроенных ІР-блоков даёт схеме прикладную направленность, увеличивая её эффективность для решения задач определённого класса. Та-

кие СБМК относят к классу платформ (Platform ASICs).

Отметим, что в случае применения структурированных БМК или ПЛИС, содержащих большое число IP-блоков, параметры разрабатываемых на их базе БИС практически не уступают чистым ASIC по быстродействию и совсем немного проигрывают в площади при существенно более низкой стоимости проектирования и изготовления кристаллов.

СБМК являются универсальной элементной базой. Они очень похожи на ПЛИС и позволяют реализовывать проекты, представленные как на структурном, так и на поведенческом уровне. Для проектирования зашивок СБМК можно использовать проектные данные, подготовленные в САПР ПЛИС.

Принципиально с помощью СБМК при технологии изготовления базовых пластин уровня 90 нм можно достигнуть следующих результатов:

- число вентилей до 5 млн.;

- быстродействие до 0,05 нс на вентиль:

- тактовые частоты до 600 МГц;

- встроенное ОЗУ до 32 Мб;

- масочное ПЗУ до 256 Мбит.

Полузаказные БИС на базе СБМК в 5–7 раз рентабельнее ПЛИС и обладают существенно более высокими параметрами.

Структурированные БМК предоставляют уникальную возможность комбинированного изготовления микросхем, при которой базовые пластины изготавливаются за рубежом по технологии с проектными нормами 40...60 нм, а изготовление конкретных зашивок осуществляется в России по технологиям, имеющим худшие проектные нормы, например 90...130 нм. Это объясняется тем, что в процессе литографии СБМК приходится стравливать стандартные программируемые перемычки, которые могут иметь не минимальные размеры.

Для организации программирования СБМК будет достаточно запустить технологическую линейку, позволяющую выполнять литографии верхнего слоя металла для пластин диаметром 200 мм, что значительно проще организации полного технологического процесса изготовления СБИС.

Пример структуры несложного структурированного БМК приведен на рис. 2, а СБМК с расширенным набором IP-блоков – на рис. 3.

# **П**РОТОТИПИРОВАНИЕ СЛОЖНЫХ СИСТЕМ НА КРИСТАЛЛЕ

Достаточно эффективным подходом, позволяющим существенно сократить расходы на отработку аппаратуры, является проведение её отладки (прототипирования) с помощью программируемой элементной базы [14, 20].

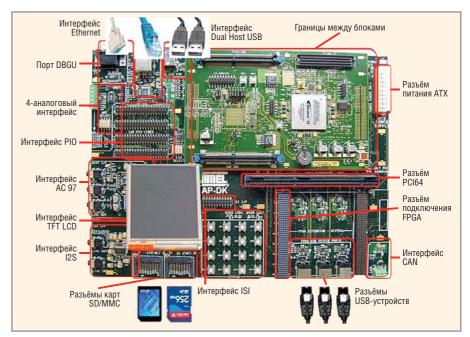

Очень интересным современным подходом в разработке сложных систем на кристалле является проведение разработки с использованием платпрототипов.

При таком подходе для облегчения процесса отработки аппаратуры разработчику предлагается на первом этапе выполнить разработку системы на полностью программируемой плате, содержащей процессор, память, массив программируемых вентилей в виде ПЛИС, а также широкий набор интерфейсных микросхем (USB, Ethernet, I2S, SPI и т.д.). Продвинутые версии таких плат могут включать также микросхемы цифроаналогового интерфейса (ЦАП, АЦП). Плата прототипирования имеет небольшие размеры и во многих случаях может работать непосредственно в разрабатываемой ап-

Рис. 4. Плата CAP-9 фирмы Progate Groop для прототипирования CHK

паратуре. Пример платы прототипирования CAP-9 фирмы Progate Groop приведён на рис. 4.

Основной особенностью данной методологии проектирования является то, что у платы прототипирования имеется двойник – СБМК, содержащий такой же набор IP-блоков, что и

сама плата. Более того, исходными данными для формирования зашивочного слоя этого СБМК является программируемая информация, полученная при отладке платы прототипирования. Пример СБМК, соответствующего плате САР-9, приведён на рис. 5.

Рис. 5. СБМК с набором ІР-блоков, совместимая с платой САР-9

Применение этой методологии позволяет вывести процесс отладки аппаратуры на принципиально новый уровень. Разработчик может получить полностью отлаженную систему без изготовления специальной элементной базы и только на последнем этапе заказать по тщательно отлаженной и отработанной информации специализированную полузаказную БИС, изготавливаемую на базе СБМК. Это позволяет избежать дорогостоящих повторных изготовлений специализированных СБИС и обеспечить быстрый вывод на рынок сложных электронных изделий.

### СБМК и нанометровые проекты СБИС

С переходом к проектированию СБИС на базе технологии с проектными нормами менее 90 нм проекты, выполненные на базе стандартных ячеек (обычные ASIC), не способны более достигать преимуществ в цене кристаллов и их быстродействии при дальнейшем уменьшении проектных норм [15, 16]. Глубоко субмикронные и нанометровые СБИС требуют нового подхода к проектированию вместо стандартных ячеек для реализации проектов на современном уровне.

Полностью заказное проектирование было предпочтительным решени-

ем до тех пор, пока оно не стало слишком длительным и дорогим процессом для большинства проектов. В это время микроэлектронная промышленность выбрала методологию стандартных ячеек ценой некоторого проигрыша в площади и быстродействии.

В процессе дальнейшего уменьшения проектных норм произошло принципиальное изменение ситуации. Задержки межсоединений между различными блоками БИС стали доминировать в общей задержке схем, размеры элементов стали меньше, чем длина волны при фотолитографии, резко возросла цена комплекта фотошаблонов и, соответственно, цена производства СБИС на стандартных ячейках. Возникла необходимость заменить стандартные ячейки в качестве базовой технологии чем-то другим. Этим другим подходом явились СБИС с программируемой структурой, в которых базовые слои и большая часть слоёв металла стандартизованы.

Около 25 лет назад стандартные ячейки начали замещать полностью заказные схемы – основную в то время методологию проектирования. В те дни стоимость полностью заказного проекта начала превышать 10 млн. долл., и сообщество разработчиков СБИС согласилось проиграть более чем вдвое в быстродействии и плот-

ности, снизив стоимость проекта примерно в 10 раз.

С тех пор стоимость проекта на стандартных ячейках опять выросла до 10 млн. долл. Снова появилась потребность перехода на новую методологию проектирования, существенно снижающую стоимость проектов, но, по возможности, без значительных потерь в быстродействии и плотности. Роль такого нового подхода сыграли БИС с программируемой архитектурой. Подмножеством этого класса схем являются СБМК, программируемые с помощью переменного слоя межслойных переходов. Такие схемы были предложены несколькими фирмами (eASIC, ViASIC, LeopardLogic) [9], а также академическими организациями (Carnegie Mellon's VPGA). Часто такие схемы называют «стандартным ме-

Непрерывное уменьшение размеров элементов привело к значительному удорожанию сверхбыстродействующих СБИС. Однако не все элементы схем уменьшаются в равной степени. Для того чтобы понять влияние этого дифференцированного уменьшения, необходимо проанализировать каждый элемент по отдельности. Обычно вся цифровая логика построена на двух элементах: транзисторы и металлические соединения. Уменьшение

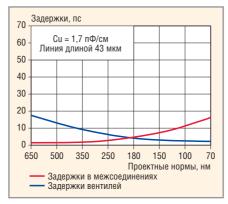

размеров транзисторов приводит к уменьшению времени их переключения. К сожалению, уменьшение размеров увеличивает сопротивление межсоединений и, сверх того, увеличивает их ёмкости, что приводит к росту задержек в межсоединениях. График этой зависимости приведён на рис. 6.

При проектной норме 180 нм проявляется первая особенность. После ряда лет доминирования транзисторных задержек непрерывное уменьшение размеров приводит к доминированию задержек, вносимых межсоединениями [1, 3]. Для борьбы с этим эффектом были разработаны дорогостоящие технологии, позволяющие уменьшить эти задержки. Для уменьшения сопротивления коммутационных проводников стали применять медь вместо алюминия, а для уменьшения паразитных ёмкостей использовать диэлектрические материалы с низкой диэлектрической проницаемостью.

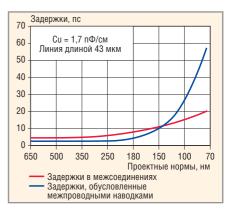

Однако, несмотря на эти усилия, задержка межсоединений в настоящее время всё ещё очень актуальна. Такое положение сохранится и в будущем. Например, при проектной норме 100 нм энергия переключения проводников в среднем в 5 раз превышает энергию переключения транзисторов, а для нормы 35 нм — в 30 раз. Более того, возникает проблема межпроводниковых наводок (проблема «целостности сигнала»). Причём с уменьшением проектных норм влияние проблемы «целостности сигнала» начинает доминировать [3].

На рис. 7 показан график зависимости задержек переключений и задержек, обусловленных фактором межпроводных наводок в зависимости от проектных норм. Эти явления приводят к существенному замедлению роста быстродействия схем при переходе к следующему уровню технологии.

В настоящее время стало совершенно ясно, что для получения проектов с небольшими, прогнозируемыми задержками необходимо заменить основной строительный блок СБИС – вентиль – на более крупный блок, позволяющий реализовывать более сложные логические функции и содержащий внутри заведомо короткие связи. Таким строительным элементом является LUT – логический примитив, выигравший в войнах FPGA. Конструирование логических функций с помощью примитивов большого размера становится гораздо более эффектив-

Рис. 6. График роста задержек в межсоединениях при уменьшении размеров

ным, чем использование многочисленных мелких вентилей, соединённых проводниками, поскольку эти проводники приводят к трудно прогнозируемым большим задержкам.

Следовательно, логика, определяемая межслойным переходом, или, в качестве альтернативы FPGA, логика, определяемая битовым потоком, будет предпочтительным вариантом для первого этапа перехода от стандартных ячеек к стандартному металлу.

Очевидно, что более крупная логика LUT делает возможной стандартизацию нижних слоёв металла, используемых для конструирования соединений логических элементов нижнего уровня. Однако реальное преимущество набора логических элементов нижнего уровня из крупных элементов заключается в её влиянии на слои трассировки. Слои, располагающиеся поверх набора логических элементов нижне-

Рис. 7. График «проблемы целостности сигнала» (межпроводниковых наводок)

го уровня, используют для соединения между собой логических ячеек и построения реальной логической схемы. Набор логических элементов нижнего уровня, построенный из повторяющихся крупных логических ячеек, допускает эффективное использование сегментированной трассировки подобно тому, как это делается в FPGA. Важным преимуществом использования крупных ячеек является меньшее число проводников, которые необходимо развести с помощью автоматических процедур размещения и трассировки, поскольку проводники, входящие в состав крупной ячейки, уже являются частью этой ячейки, спроектированной вручную. При использовании крупных ячеек можно использовать формальные методы буферизации сигналов, распространяющихся по длинным связям [19].

Продолжение следует