# Микроконтроллер 1867ВЦ5Т с 16-разрядным процессором ЦОС и флэш-памятью для систем цифрового управления электродвигателями

Валерий Крюков, Владимир Горохов, Николай Данильченко (г. Воронеж)

В статье рассмотрена архитектура микроконтроллера 1867ВЦ5Т для специальных применений типа Motor Control с 16-разрядным процессором цифровой обработки сигналов, флэш-памятью и набором периферийных устройств, адаптированных для управления электродвигателями.

Семейство 1867 процессоров цифровой обработки сигналов, [1], пополнилось микросхемой 1867ВЦ5Т [2–4] типа Motor Control, предназначенной для построения высокопроизводительных систем цифрового управления электрическими двигателями различных типов.

Микроконтроллер 1867ВЦ5Т (далее микроконтроллер, МК) содержит 16-разрядный процессор цифровой обработки сигналов с архитектурой ядра процессора 1867ВМ2, встроенную флэш-память программ, менеджер событий, полный набор периферийных устройств, адаптированных для управления двигателями, а также набор стандартных последовательных интерфейсов, ориентированных на эффективную работу в распределённых системах управления (встроенный коммуникационный - SCI, периферийный - SPI). Последовательные интерфейсы, интерфейс с внешней памятью и внешними устройствами дают возможность разработчику проектировать сложные системы управления, обеспечивающие дружественный интерфейс с оператором (возможность подключения пультов оперативного управления любой сложности) и взаимодействие с дополнительным технологическим оборудованием и устройствами ввода/вывода.

Высокая производительность МК (до 20 MIPS), менеджер событий, работаю-

щий независимо от центрального процессора, и встроенная флэш-память объёмом 16 Кслов позволяют проектировать высокоэффективные компактные устройства управления с активными цифровыми фильтрами, электроприводами различной конструкции, преобразователями частоты и матричными преобразователями.

Оптимизированная архитектура блока менеджера событий предназначена для прямого цифрового управления приводами всех типов на базе асинхронных, синхронных, шаговых, коллекторных и бесколлекторных двигателей постоянного тока; построения двух- и многодвигательных систем привода, двух- и многоинверторных систем, полностью управляемых силовых преобразователей, преобразователей с активными входными цифровыми фильтрами, преобразователей частоты с непосредственной связью, матричных преобразователей и т.п.

Микроконтроллер 1867ВЦ5Т может заинтересовать разработчиков, которым требуется высокая производительность центрального процессора для обеспечения эффективного прямого цифрового управления одновременно всеми ключами силового преобразователя, а также эффективная рекуперация энергии в тормозных режимах работы привода.

Флэш-память МК выполнена по 0,35-мкм КМОП технологии, а процес-

сорное ядро и встроенная периферия выполнены по 0,5-мкм высокопроизводительной статической КМОП технологии. Программирование флэшпамяти МК осуществляется через SCIпорт или JTAG-порт и не требует дополнительного источника питания.

Микроконтроллер 1867ВЦ5Т предназначен для работы в специальной аппаратуре и выпускается в четырёхстороннем плоском металлокерамическом корпусе типа 4229.132-3. В таблице приведены основные технические характеристики микроконтроллера.

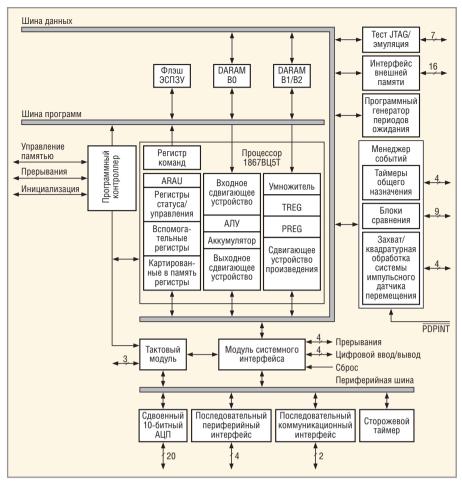

На рисунке приведена функциональная блок-схема микроконтроллера, которая иллюстрирует его высокоуровневую архитектуру. Микроконтроллер состоит из четырёх основных блоков:

- центрального процессора;

- внутренней памяти с двойным доступом (DARAM);

- энергонезависимой флэш-памяти программ;

- периферийных устройств, подключенных к периферийной шине.

Микроконтроллер имеет несколько архитектурных особенностей, которые определяют его работу на системном уровне: карту памяти, устройство формирования сигнала сброса микроконтроллера, сигналы прерывания, устройство цифрового ввода/вывода, генератор синхронизации и энергосберегающие режимы функционирования.

Ядро процессора микроконтроллера включает:

- 32-битное центральное арифметико-логическое устройство (АЛУ);

- 32-битный аккумулятор;

- параллельный умножитель 16× 16 бит с 32-битным результатом, который сохраняется в регистре PREG;

- три устройства сдвига, которые не требуют дополнительных циклов для сдвига данных на входе и выходе АЛУ, а также на выходе умножителя:

- восемь 16-битных вспомогательных регистров со специализированным арифметическим блоком (ARAU) для вычисления косвенного адреса памяти данных, который работает независимо от АЛУ.

Ядро центрального процессора микроконтроллера имеет модифицированную многошинную гарвардскую архитектуру с раздельными шинами памяти программ и памяти данных, что позволяет одновременно считывать команды и данные, повышая его производительность. Команды выполняются процессором параллельно на четырёхуровневом конвейере. Набор инструкций содержит команды обмена данными между различными областями памяти, что позволяет размещать коэффициенты цифровых регуляторов и цифровых фильтров как в памяти программ, так и в памяти данных.

Система команд микроконтроллера оптимизирована для эффективного решения задач цифровой фильтрации и управления в реальном времени. В частности, легко реализуются кольцевые буферы на основе использования специального метода адресации операндов с реверсированием направления распространения бита переноса. Программное управление (программный контроллер) включает четырёхуровневый конвейер, позволяющий повысить производительность микроконтроллера, восьмиуровневый аппаратный стек и шесть внешних прерываний (прерывание от схемы защиты по электропитанию, сброс, NMI и три маскируемых прерывания). Запросы прерываний поступают как от встроенных на кристалле периферийных устройств, так и от внешних источников прерываний. Источники прерывания ранжированы по приоритету от 1 до 40.

Система команд МК совместима по исходному коду с ИС типа М1867ВМ1, 1867ВМ2 и с семейством ЦПОС ТМS320С1х/2х, ТМS320F2хх фирмы Texas Instruments [5], имеет эффективную реализацию операции повзторения и одноцикловые инструкции умножения с накоплением, содержит инструкции перемещения блока памяти из памяти данных в па-

Функциональная блок-схема микроконтроллера 1867ВЦ5Т

мять программ и наоборот, имеет эффективную индексную адресацию данных, включая битреверсивную индексную адресацию данных для эффективной реализации алгоритма быстрого преобразования Фурье по основанию 2. Микроконтроллер выполняет большинство команд за один машинный такт (50 нс), что эквивалентно производительности до 20 MIPS.

Внутрикристальная память микроконтроллера с двойным доступом (DARAM) включает 256 слов памяти данных/программ – блок (В0) и 288 слов памяти данных (блоки В1, В2). Главной особенностью работы DARAM является запись и чтение из ОЗУ в течение одного машинного такта. С учётом раздельного доступа к памяти программ и памяти данных, за один машинный такт возможно

## Технические характеристики микроконтроллера 1867ВЦ5Т

| Интерфейс внешней памяти                                     | Есть       |

|--------------------------------------------------------------|------------|

| Менеджер событий                                             | Есть       |

| Число таймеров общего назначения                             | 3          |

| Число каналов сравнения/ШИМ                                  | 9/12       |

| Число каналов захвата/ввода «квадратурных» сигналов          | 4/2        |

| Сторожевой таймер                                            | 1          |

| Таймер реального времени                                     | 1          |

| Аналого-цифровой преобразователь (10-разрядный)              | 2          |

| Число каналов                                                | 16         |

| Время преобразования (минимальное)                           | 6,1 мкс    |

| Последовательный периферийный интерфейс (SPI)                | 1          |

| Последовательный коммуникационный интерфейс (SCI)            | 1          |

| Число линий дискретного ввода/вывода                         | 28         |

| Число внешних прерываний                                     | 6          |

| Напряжение питания                                           | 5 B ± 10%  |

| Температура эксплуатации                                     | -6080°C    |

| Корпус (металлокерамический четырёхсторонний плоский корпус) | 4229.132-3 |

сразу три обращения к памяти. Эта память используется, главным образом, для хранения и выборки констант и переменных. Один из банков (В0) DARAM объёмом 256 слов в процессе выполнения программы может динамически переконфигурироваться для использования либо в качестве памяти данных, либо в качестве памяти программ. Последняя возможность обеспечивает подзагрузку фрагментов программного кода из внешней, медленной памяти для ускоренного выполнения во встроенной памяти.

Внутрикристальная флэш-память (ЭСПЗУ) [6] объёмом 16 Кслов является альтернативой масочному ПЗУ. Она является энергонезависимой и допускает перепрограммирование непосредственно в разработанном изделии – либо по последовательному каналу связи SCI, либо через JTAG-порт от внутрисхемного эмулятора. Программирование флэш-памяти микроконтроллера не требует никаких специальных программаторов, т.к. алгоритмы стирания и программирования реализуются непосредственно центральным процессором МК.

Микроконтроллер поставляется с записанной во флэш-память программой первоначальной загрузки (bootloader) [7], позволяющей загружать и перепрограммировать флэшпамять с помощью сервисной программы [8]. При использовании внутрисхемного эмулятора (через JTAG-порт) для программирования флэш-памяти, программные модули, необходимые для реализации процедуры стирания и записи данных во флэш-память, предварительно загружаются во внутрикристальное программное ОЗУ микроконтроллера, где позже выполняются.

Программирование флэш-памяти не требует дополнительного источника питания, т.к. осуществляется от 5-В источника питания микроконтроллера. Выбор режима работы (выполнение программы пользователя или программирование флэш-памяти) обеспечивается подачей соответствующего потенциала на вывод ВІО# микроконтроллера [8].

Флэш-память секционирована, причём каждая секция может быть индивидуально очищена и запрограммирована либо защищена от стирания и записи. Наличие флэш-памяти удобно при разработке контролле-

ров-прототипов, а также для гибких и часто перенастраиваемых однокристальных систем управления.

Модуль интерфейса внешней памяти реализует 16-битную шину адреса, 16-битную шину данных и сигналы управления, которые позволяют отдельно адресовать внешнюю память программ, данных и пространство ввода/вывода. Программный генератор периодов ожидания поддерживает аппаратную генерацию периодов ожидания при обращении к медленной и, соответственно, недорогой памяти. Микроконтроллер может адресовать до 224 Кслов (64 Кслов программного пространства, 64 Кслов пространства данных. 64 Кслов пространства ввода/вывода, 32 Кслов глобального пространства). Глобальное пространство может быть разделено между другими микроконтроллерами или активными устройствами с целью создания мультипроцессорных систем.

Управление доступом к глобальной памяти должно осуществляться внешней схемой — «арбитром», который по сигналу ВR# от микроконтроллера либо разрешает (формирует высокий уровень сигнала READY), либо запрещает (формирует низкий уровень сигнала READY) доступ к глобальной памяти. Размер (от 256 до 32 Кслов) глобального (разделяемого) пространства памяти может программироваться установкой соответствующего значения в регистре GREG (на блок-схеме не показан) [3].

Менеджер событий включает [4]:

- 12 каналов с широтно-импульсной модуляцией (PWM);

- три 16-битных универсальных таймера с шестью режимами работы, включающие непрерывный счёт в прямом направлении и непрерывный счёт в прямом/обратном направлении;

- три 16-битных блока полного сравнения с возможностью задания «мёртвого» времени;

- три 16-битных блока простого сравнения;

- четыре блока захвата, два из которых имеют интерфейс для обработки сигналов от импульсного датчика положения.

Менеджер событий предоставляет в распоряжение пользователя уникальные возможности управления двигателями. Например, используя таймеры, разработчик может программно определить скорость вращения каждого вала системы привода и по разности скоростей реализовать эффективное управление, – например, демпфирование упругих колебаний в механической части привода, безударную выборку зазоров и синхронизацию вращения колес, разворот на месте, защиту от заноса, а также решать другие специфические задачи, присущие современным тяговым приводам.

Наличие большого числа каналов формирования ШИМ-сигналов (12 каналов) открывает новые возможности управления системами, способными возвращать энергию торможения в сеть, — приводами подъёмных механизмов кранов, лифтов, шахтных механизмов и т.д. В этом случае МК может одновременно в реальном времени управлять входным и выходным преобразователями, обеспечивая эффективную работу привода во всех четырёх квадрантах.

Микроконтроллер содержит два 10-разрядных независимых АЦП, которые могут запускать преобразование от внешнего или от внутреннего события. Преобразование может выполняться как в непрерывном, так и в старт-стопном режиме. Аналоговые входы АЦП могут рассматриваться как 16 независимых каналов или как две группы каналов по 8 входов. АЦП могут работать в режиме автоматического сканирования, когда выполняется последовательный запуск аналого-цифрового преобразования по заранее заданным пользователем каналам, т.е. имеется возможность реализовать «измерительную сессию».

Уникальные возможности АЦП позволяют эффективно решать сложные задачи прямого цифрового управления током и моментом в современных приводах переменного тока. Прежде всего, речь идет о возможности реализации нескольких «псевдоодновременных» выборок данных, а также о возможности получения множественных выборок по одним и тем же каналам с целью увеличения разрешения или эффективной цифровой фильтрации.

Микроконтроллер имеет 28 цифровых мультиплексированных выводов, которые могут индивидуально программироваться в качестве входов или выходов.

Тактовый модуль содержит схему фазовой автоподстройки частоты так-

тового генератора (PLL) и схему программного управления этим модулем.

Модуль сторожевого таймера (WD) включает программируемый сторожевой таймер с временем формирования сигнала сброса от 15,63 мс до 1 с и блок таймера реального времени (RTI). Эти два блока работают независимо от центрального процессора и могут быть использованы для устранения ошибочной работы микроконтроллера.

Последовательный коммуникационный интерфейс (SCI) реализует обмен данными с асинхронной периферией на 65 000 программируемых скоростях [4].

Последовательный периферийный интерфейс (SPI) реализует высокоскоростной синхронный обмен данными [4] с аналогичными устройствами.

Микроконтроллер обеспечивает режим отладки в реальном времени с помощью внутрисхемного эмулятора и сканирующих цепочек, которые подключаются через JTAG-порт (IEEE 1149.1) к эмулятору XDS5 $10^{\text{TM}}$ .

Микроконтроллер имеет полный набор кросс-средств и эффективных средств отладки как программного, так и аппаратного обеспечения, которые включают:

- ассемблеры, компоновщики, Сикомпиляторы, отладчики в исходных кодах от фирмы Texas Instruments и третьих фирм;

- программно-логическую модель процессора (симулятор);

- устройство для работы с внутрисхемным эмулятором типа XDS5 $10^{\text{гм}}$  или XDS5 $10^{\text{PP}^{\text{TM}}}$  (от фирмы Texas Instruments);

- интегрированные среды разработки программного обеспечения Code Composer™ от Texas Instrument.

Для разработки и отладки аппаратуры и программных средств на базе микроконтроллера 1867ВЦ5Т имеются следующие отладочные средства:

- оценочный модуль [9];

- модуль разработки c24x EVM (фирма Texas Instrument);

- модуль разработки EVM320F240 (фирма Spectrum Digital [8]).

Техническая поддержка и консультирование разработчиков по применению микроконтроллера 1867ВЦ5Т осуществляется фирмой «Сканти-РУС» [11] и учебно-научно-консультационным центром Texas Instruments – МЭИ [12].

Техническая документация на микроконтроллер 1867ВЦ5Т находится на интернет-сайте[9].

# Литература

- Крюков В., Ачкасов В., Стоянов А., Горохов В.

Процессоры цифровой обработки сигналов

серии 1867. Chip News. 2004. № 6. С. 37–39.

- 2. Микросхемы интегральные 1867BЦ5Т. Техническое описание. КФДЛ.431299.013TO.

- Микросхемы интегральные 1867ВЦ5Т.

Описание центрального процессора и системы команд. КФДЛ.431299.013.1TO.

- 4. Микросхемы интегральные 1867ВЦ5Т. Описание периферийных устройств. КФДЛ.431299.013.2TO.

- 5. www.ti.com.

- 6. Микросхемы интегральные 1867ВЦ5Т. Встроенная flash-память ЭСППЗУ. КФДЛ.431299.013.3TO.

- 7. Микросхемы интегральные 1867ВЦ5Т. Загрузчик. Описание программного обеспечения. КФДЛ.431299.013Д4.

- 8. Перепрограммирование ЕЕРROM 1867ВЦ5Т. Описание программы. РОФ. КФДЛ.00107-01 13 01.

- 9. www.niiet.ru.

- 10. www.spectrumdigital.com.

- 11. www.scanti.ru.

- 12. www.motorcontrol.ru.

# DC/DC-преобразователи для жёстких условий эксплуатации

THE XPERTS IN POWER

- Диапазон рабочих температур от -40 до +100°С (основание корпуса)

- Высокий показатель надёжности

- Стойкость к внешним воздействующим факторам

- Стандартный набор сервисных функций

# 120 BT

- Небольшие габариты: 95 × 11,5 × 65 мм

- КПД до 82%

- Диапазон входных напряжений 9,5...40 В

Выходные напряжения 3,3; 5; 12; 15 и 24 В

- Защита от перегрузки, перенапряжения, короткого замыкания, перегрева; параллельная работа до 4 модулей.

- параллельная работа до 4 модулей внешняя обратная связь

- MTBF > 1 000 000 ч

# 50/75/100/150/200 BT

- Гальваническая развязка: вход-выход 1500 В (постоянное напряжение)

- КПД до 85%

- Диапазоны входных напряжений: 9...36, 18...75, 18...36 и 36...75 В

- Одноканальные и двухканальные модели

- Защита от короткого замыкания нагрузки длительного действия

- Экранированный с пяти сторон корпус

- MTBF >1 000 000 ч (MIL-HDBK-217F, при 25°C)

реклама

Официальный дистрибьютор компании XP Power в России и странах СНГ — компания ПРОСОФТ

Тел./факс: (495) 234-0636/0640 info@prosoft.ru • www.prosoft.ru