## Самосинхронизирующиеся коды и их преобразователи

(часть 5)

## Сергей Гончаров, Геннадий Шишкин (Нижегородская обл.)

Рассмотрены способы построения и схемотехнические решения кодирующих и декодирующих устройств самосинхронизирующегося фазоманипулированного кода.

Для передачи информации по последовательным каналам связи широко используются униполярные самосинхронизирующиеся коды, которые не требуют дополнительных линий связи для тактовых сигналов.

Одним из способов построения самосинхронизирующихся кодов является увеличение скорости передачи сигналов по сравнению со скоростью передачи информации (введение сигнальной избыточности). Наиболее известными типами построенных таким образом кодов являются фазоманипулированный и частотно-манипулированный коды [1].

При использовании фазоманипулированного кода (ФМ-кода) лог. 1 представляется отрицательным перепадом сигнала в середине тактового интервала, а лог. 0 — положительным перепадом сигнала. При этом информационный перепад сигнала в середине тактового интервала является обязательным. Тактовый перепад сигнала в начале тактового интервала формируется только в том случае, когда в предыдущем и последующем тактах присутствует одинаковая информация. При этом если в обоих тактах передаётся лог. 0, формируется отрицательный перепад сигна-

ла, а при передаче лог. 1 – положительный перепад сигнала. Следовательно, тактовый перепад сигнала является необязательным и может иметь любое из двух направлений. При этом максимальное расстояние между перепадами сигнала не превышает длительности T тактового интервала.

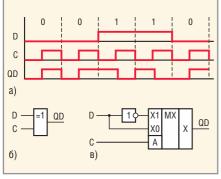

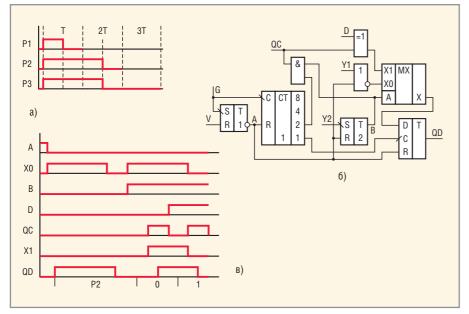

Способ формирования ФМ-кода иллюстрирует рисунок 1а, где D – входной двоичный код, С – тактовые импульсы, QD – выходной ФМ-код. Формирователь ФМ-кода может быть построен на основе логического элемента «исключающее ИЛИ» в соответствии с рисунком 16 или на основе мультиплексора в соответствии с рисунком 1в [2]. Недостатком представленных схем является возможность формирования на выходе помех в случае относительного смещения фронтов входного кода и тактовых импульсов.

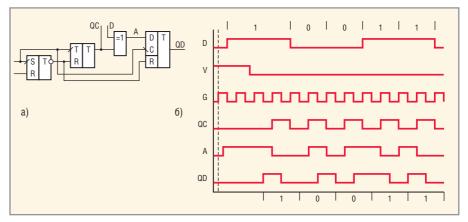

В кодирующем устройстве на основе элемента «исключающее ИЛИ» исключение помех может быть достигнуто при построении схемы в соответствии с рисунком 2а. Временные диаграммы сигналов в различных точках схемы приведены на рисунке 2б. Период повторения импульсов задающего генератора на входе G равен длительности

тактового импульса. В режиме ожидания все тригтеры удерживаются в лог. 0 сигналом на управляющем V-входе. На выходах QC и QD присутствует лог. 0, на D-входе устройства может присутствовать лог. 1 первого разряда входного кода, который без изменения проходит в точку A.

При поступлении разрешающего сигнала на V-вход, ближайшим положительным перепадом импульса генератора переключается RS-триггер и разрешает переключение счётного и **D-триггера.** Затем отрицательным перепадом импульса генератора D-триггер переключается в лог. 1, а положительным перепадом переключается счётный триггер, формируя на выходе ОС положительный перепад тактового импульса и изменяя сигнал в точке А. Следующим отрицательным перепадом D-тригтер переключается в лог. 0, формируя на выходе QD отрицательный перепад напряжения, соответствующий лог. 1 ФМ-кода. Положительный перепад сигнала генератора переключает счётный тригтер, заканчивая тактовый импульс на выходе QC и вызывая сдвиг информации на D-входе. Далее формирование ФМ-кода происходит аналогичным образом в соответствии с рисунком 26; D-тригтер работает в режиме задержки входного информационного сигнала на величину длительности импульса генератора.

Схема кодирующего устройства, аналогичная рисунку 2a, может быть пост-

Рис. 1. Формирователи ФМ-кода

(а) временные диаграммы ФМ-кода,

(б, в) — варианты схемной реализации формирователей ФМ-кода

Рис. 2. Кодирующее устройство ФМ-кода на основе элемента «исключающее ИЛИ»

(а) схема кодирующего устройства, (б) временные диаграммы ФМ-кода

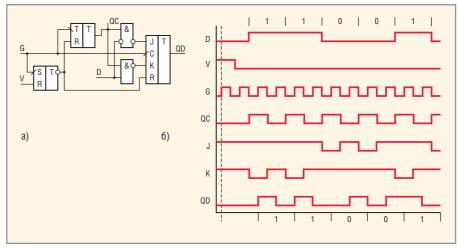

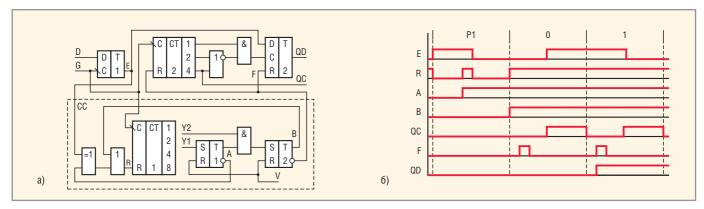

роена на основе ЈК-триггера в соответствии с рисунком 3а. При этом учитывается, что информационные перепады в ФМ-коде обязательны, а уровень сигнала в первой половине тактового интервала совпадает с уровнем входного сигнала. В режиме ожидания RSтриггер, а следовательно, счётный и ЈКтриггер, удерживаются в состоянии лог. 0 сигналом лог. 1 по V-входу. На выходах QC и QD присутствует лог. 0. При этом на ЈК-входах присутствует лог. 1. На G-вход поступают импульсы задающего генератора, период повторения которых равен длительности тактового импульса. Временные диаграммы сигналов в различных точках показаны на рисунке 3б.

При поступлении разрешающего сигнала по V-входу ближайшим положительным перепадом импульса генератора переключается RS-триггер и разрешает переключение счётного и ЈК-триггера. Отрицательным перепадом импульса переключается счётный триггер, формируя положительный перепад тактового импульса на выходе ОС. При этом на D-вход продвигается информация первого разряда входного кода, например, в виде лог. 1, а на Квходе ЈК-тригтера устанавливается лог. 0. Поэтому положительным перепадом следующего импульса генератора ЈКтриггер переключается в лог. 1. Отрицательным перепадом данного импульса переключается счётный триггер, формируя отрицательный перепад тактового импульса и восстановление лог. 1 на К-входе ЈК-триггера.

Положительным перепадом следующего импульса ЈК-тригтер переключается, формируя информационный перепад лог. 1 ФМ-кода на выходе QD. Отрицательный перепад данного импульса переключает счётный триггер, формируя положительный перепад тактового импульса, вызывающего продвижение информации второго разряда входного кода на вход D, и создавая лог. 0 на К-входе ЈК-триггера. Далее устройство работает аналогичным образом в соответствии с рисунком 3б. Информационные перепады выходного кода формируются ЈК-триггером в счётном режиме, а тактовые перепады лишь подготавливают направление информационных перепадов.

Исключение помех на выходе QD в описанных выше схемах (см. рис. 2а и 3а) достигается разнесением во времени моментов формирования фронтов тактовых импульсов и перепадов на-

Рис. 3. Кодирующее устройство ФМ-кода на основе ЈК-триггера

(а) схема кодирующего устройства, (б) временные диаграммы

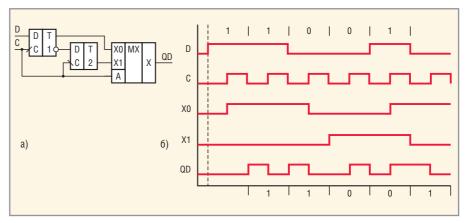

Рис. 4. Кодирующее устройство ФМ-кода на основе мультиплексора

(а) схема кодирующего устройства, (б) временные диаграммы

пряжения выходного ФМ-кода. Аналогичным образом исключение помех может быть достигнуто при построении кодирующего устройства на основе мультиплексора. Однако в последнем случае исключение помех может быть достигнуто также при построении кодирующего устройства в соответствии с рисунком 4а. Соответствующие временные диаграммы сигналов в различных точках схемы приведены на рисунке 46.

В режиме ожидания на тактовом (С) и информационном (D) входах присутствует лог. 0. Тригтеры установлены в лог. 0. На выход QD проходит лог. 0 с входа Х0 мультиплексора. При поступлении на D-вход, например, лог. 1 состояние схемы не изменяется. По положительному перепаду первого тактового импульса мультиплексор подключает на выход лог. 0 со входа Х1. Одновременно переключается первый триггер, формируя лог. 1 на входе Х0 мультиплексора. По отрицательному перепаду первого тактового импульса сигналом с инверсного выхода первого триггера подтверждается исходное состояние второго триггера, а мультиплексор подключает к выходу лог. 1 первого триггера.

По положительному перепаду второго тактового импульса мультиплексор подключает на выход лог. 0 со входа X1, формируя отрицательный перепад, соответствующий лог. 1 входного кода. Одновременно переключается первый тригтер в состояние, соответствующее второму разряду входного кода. По отрицательному перепаду второго тактового импульса сигналом с инверсного выхода первого триггера переключается второй тригтер, а мультиплексор подключает к выходу сигнал первого триггера. Далее устройство работает аналогичным образом, формируя на выходе задержанный на один тактовый интервал ФМ-код, соответствующий входному коду. Первый и второй Dтриггеры в данной схеме работают в режиме регистра сдвига с двухтактным управлением положительным и отрицательным фронтами тактового импульса. Для исключения помех мультиплексор всегда отключает выход QD от переключаемого тригтера. При этом

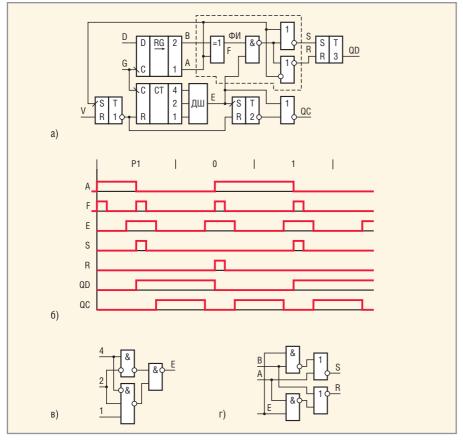

Рис. 5. Кодирующее устройство ФМ-кода

(а) временные диаграммы реализации признака начала кода, (б) схема формирования признака начала кода, (в) временные диаграммы работы кодирующего устройства

быстродействие мультиплексора должно быть не хуже быстродействия триггера.

Из рисунка 1а следует, что тактовый перепад не формируется в начале информационной посылки, если в первом такте передаётся информация лог. 0, что не позволяет в этом случае определить начало кодовой последовательности. Указанное свойство ФМ-кода требует для формирования тактового перепада передачу признака начала кодовой последовательности, например, в виде лог. 1 или специального сигнала, временные параметры которого отличаются от параметров ФМкода. В последнем случае обеспечивается надёжная обработка информации при её непрерывном поступлении, особенно с переменной длительностью информационных посылок.

Простейшие варианты реализации признака начала кода показаны на рисунке 5а. При этом сигнал Р1 является лог. 1 и занимает один тактовый интервал *Т*; длительность импульса равна длительности паузы. Сигнал Р2 занимает два тактовых интервала, а длительность импульса, в отличие от ФМ-кода, – полтора тактовых интервала.

Сигнал Р3 имеет два отличительных признака и занимает три тактовых ин-

Таблица 1. Способ подключения входов Y1 и Y2 к выходам счётчика импульсов (см. рис. 5б)

| Y\P | P1 | P2   | P3   |

|-----|----|------|------|

| Y1  | 2  | 2\$4 | 2\$4 |

| Y2  | 2  | 4    | 4\$8 |

тервала, а длительность паузы и длительность импульса – по 1,5 тактовых интервала.

При использовании в качестве признака начала кода сигнала Р1 можно формировать дополнительный сигнал лог. 1 нулевого разряда в начале каждой информационной посылки, поступающей на вход кодирующего устройства. При этом может использоваться любое из кодирующих устройств (см. рис. 2а, 3а или 4а).

Кодирующее устройство ФМ-кода со схемой формирования признака начала кода приведено на рисунке 56. Способ подключения входов Y1 и Y2 схемы к выходам счётчика импульсов для формирования выбранного признака начала кода определяется таблицей 1, где цифры 2, 4 и 8 обозначают выходные сигналы соответствующих разрядов счётчика.

Работа устройства при формировании сигнала Р2 поясняется временными диаграммами на рисунке 5в, где X0 и X1 – входы мультиплексора.

В режиме ожидания на управляющем V-входе присутствует лог. 1, удерживающая первый RS-триггер, а следовательно, и второй RS-триггер, D-триггер и счётчик импульсов в лог. 0. На информационном D-входе, на тактовом (QC) и информационном (QD) выходах присутствует лог. 0. На G-вход поступают импульсы задающего генератора, период повторения которых равен T/4.

При поступлении на V-вход лог. 0 первый RS-триггер ближайшим отри-

цательным фронтом импульса генератора переключается в лог. 1, разрешая переключение счётчика и остальных триттеров. Одновременно лог. 0 с инверсного выхода первого RS-триттера вызывает переключение элемента ИЛИ-НЕ в лог. 1, которая со входа X0 мультиплексора поступает на информационный вход D-триттера.

Далее счётчик начинает переключаться по отрицательному фронту входных импульсов. Ближайшим положительным фронтом с выхода первого разряда счётчика D-триггер переключается в лог. 1, формируя положительный перепад напряжения на выходе QD. При переключении счётчика на выходе второго разряда формируются импульсы с периодом повторения, равным тактовому интервалу. Через 1,5 тактовых интервала второй разряд счётчика переключается в лог. 1, которая проходит на вход Ү1, вызывая переключение элемента ИЛИ-НЕ в лог. 0. Уровень лог. 0 со входа Х0 мультиплексора поступает на информационный вход D-триггера, который (с задержкой на период повторения входных импульсов) переключается в лог. 0, вызывая окончание положительного импульса сигнала Р2 на выходе QD.

Через два тактовых интервала переключается в лог. 0 третий разряд счётчика, вызывая переключение второго RS-триггера в лог. 1, которая разрешает прохождение импульсов с выхода второго разряда счётчика через элемент И на выход QC и на вход элемента «исключающее ИЛИ». Одновременно второй RS-триггер переключает мультиплексор, запрещая прохождение на информационный вход D-триггера сигнала Р2 и разрешая прохождение сигналов с выхода элемента «исключающее ИЛИ», формирующего ФМ-код в соответствии с рисунком 1а с помощью сигнала QC. Сигнал QC определяет также моменты смены информации на Dвходе. При этом моменты смены информации на выходе QD задержаны относительно фронтов сигналов на выходах элементов ИЛИ-НЕ и «исключающее ИЛИ», что гарантирует отсутствие помех на выходе устройства.

Таким образом, представленное устройство обеспечивает формирование выбранного варианта признака начала кода и преобразование входного двоичного кода в ФМ-код с исключением влияния состязаний фронтов на сигналы по выходу QD.

Рис. 6. Декодирующее устройство с анализом уровня входного сигнала

(а) схема декодирующего устройства, (б) временные диаграммы декодирующего устройства

При построении декодирующих устройств ФМ-кода необходимо обеспечить привязку принимаемой информации к внутренней шкале времени по первому тактовому перепаду, создаваемому признаком начала кода. В качестве признаков передаваемой в каждом такте информации можно использовать не только направление перепада сигнала в середине тактового интервала, но и уровень сигнала в первой половине тактового интервала, всегда совпадающий с передаваемой информацией.

Декодирующее устройство с формированием выходного кода по результатам анализа логического уровня входного сигнала в первой половине каждого тактового интервала показано на рисунке ба, где СС – схема селекции признака начала кода. Способы формирования сигналов на входах Y1 и Y2 для селекции выбранного варианта признака начала кода приведены в таблице 2, где 1, 2, 4, 8, 16 – выходные сигналы соответствующих разрядов первого счётчика. Временные диаграммы сигналов в различных точках схемы при использовании

признака начала кода Р1 приведены на рисунке 6б.

В исходном состоянии первый D-триггер поддерживается в лог. 0 сигналом по D-входу с помощью импульсов задающего генератора, поступающих на G-вход с периодом повторения T/8. Первый и второй RS-тригтеры установлены в лог. 0 внешним сигналом по V-входу. При этом второй D-тригтер и второй счётчик удерживаются в лог. 0 сигналом с инверсного выхода второго RS-тригтера, а сигнал с инверсного выхода первого RS-тригтера через элементы «исключающее ИЛИ» и ИЛИ

Рис. 7. Декодирующее устройство с анализом перепада сигнала

- (а) схема декодирующего устройства, (б) временные диаграммы декодирующего устройства,

- (в) схема дешифратора ДШ, (г) вариант схемы формирователя импульсов

проходит на R-вход первого счётчика, удерживая его в лог. 0. На тактовом (QC) и информационном (QD) выходах присутствует лог. 0.

При поступлении на D-вход сигнала лог. 1 первый D-триггер переключается в лог. 1 отрицательным фронтом импульса генератора и далее отслеживает состояние сигнала на D-входе. Положительный перепад сигнала с выхода первого D-триггера поступает на вход элемента «исключающее ИЛИ» и переключает его в состояние лог. 0, разрешающее переключение первого счётчика.

После переключения первого и второго разрядов счётчика в лог. 1 третьим импульсом генератора первый RS-триттер устанавливается в лог. 1, разрешающую прохождение сигнала со входа Y2 через элемент И. Одновременно лог. 0 с инверсного выхода первого RS-триттера поступает на вход элемента «исключающее ИЛИ», пере-

Таблица 2. Способы формирования сигналов на входах Y1 и Y2 (см. рис. 6a)

| Y\P | P1   | P2      | P3      |

|-----|------|---------|---------|

| Y1  | 1\$2 | 1\$2\$8 | 1\$2\$8 |

| Y2  | 4    | 4       | 4\$8    |

ключая его в лог. 1, которая проходит на R-вход первого счётчика, устанавливая его в лог. 0.

После этого положительный импульс на D-входе устройства заканчивается, и первый D-триггер четвёртым импульсом генератора устанавливается в лог. 0, переключая элемент «исключающее ИЛИ» в лог. 0 и разрешая переключение первого счётчика. Затем третий разряд первого счётчика восьмым импульсом генератора в конце первого тактового интервала переключается в лог. 1, которая проходит через элемент И, переключая в лог. 1 второй RS-триггер. Уровень лог. 1 с его прямого выхода проходит через элемент ИЛИ на R-вход первого счётчика, блокируя его в состоянии лог. 0, а лог. 0 с его инверсного выхода поступает на R-входы второго счётчика и второго D-триггера, разрешая их переключение и формирование сигналов на выходах QC и QD.

Контроль признаков начала кода Р2 и Р3 производится схемой селекции аналогичным образом. При этом первый RS-триггер переключается одиннадцатым импульсом, а второй RS-триггер шестнадцатым импульсом при контроле Р2 и двадцать четвёртым им-

пульсом при контроле Р3 после промежуточного обнуления первого счётчика

Далее производится преобразование входного кода. Для этого второй счётчик с помощью дешифратора формирует в начале каждого тактового интервала (с задержкой на период повторения импульсов генератора) опросный импульс с длительностью в один период повторения импульсов генератора, который поступает на тактовый вход второго D-триггера и вызывает установку его в состояние, соответствующее уровню сигнала на Dвходе устройства, формируя сигналы на информационном выходе QD. Тактовые импульсы на выходе QC формируются третьим разрядом первого счётчика. После приёма всех разрядов информационной посылки устройство устанавливается в исходное состояние положительным импульсом по V-входу.

Из рисунка ба видно, что реализация схемы селекции признака начала кода требует существенных схемных затрат даже при использовании признака начала кода Р1, совпадающего по структуре с лог. 1 ФМ-кода. Уменьшение затрат может быть достигнуто при восприятии Р1 как дополнительного (нулевого) разряда ФМ-кода с формированием соответствующих сигналов на выходах QC и QD, которые - после контроля поступления - могут быть проигнорированы при дальнейшей обработке информации, например, путём записи информации в регистр сдвига, количество разрядов которого равно количеству информационных разрядов входного кода.

Пример схемной реализации соответствующего декодирующего устройства, использующего в качестве признака передаваемой в каждом такте информации полярность перепада сигнала в середине тактового интервала, представлен на рисунке 7а. Временные диаграммы сигналов в различных точках схемы приведены на рисунке 76.

В исходном состоянии первый RS-триггер установлен в лог. 0 сигналом по V-входу и удерживает в лог. 0 счётчик импульсов и второй RS-тригтер. Регистр сдвига установлен в лог. 0 сигналом лог. 0 по D-входу с помощью импульсов задающего генератора, поступающих на G-вход с периодом повторения *T*/8. На выходе QC присутствует лог. 0. Третий RS-триггер может на-

ходиться в любом состоянии; при необходимости он может быть установлен в лог. 0 сигналом с инверсного выхода первого RS-тригтера.

При поступлении на D-вход устройства лог. 1 нулевого разряда первый разряд регистра по отрицательному фронту импульса генератора переключается в лог. 1 и устанавливает в лог. 1 первый RS-триггер, сигнал с инверсного выхода которого разрешает переключение счётчика импульсов и второго RS-триггера. При дальнейшем переключении регистра элемент «исключающее ИЛИ» формирователя импульсов (ФИ) формирует в точке F импульсы положительной полярности длительностью, равной периоду повторения импульсов задающего генератора, по каждому из перепадов сигнала на D-входе.

Счётчик импульсов с помощью дешифратора ДШ, схема которого приведена на рисунке 7в, формирует стробирующие импульсы, позволяющие выделить с помощью элемента И-НЕ из всех импульсов в точке F импульсы, соответствующие информационным перепадам. Указанные импульсы, в зависимости от полярности перепада, направляются сигналом с выхода первого разряда регистра с помощью элементов ИЛИ-НЕ на соответствующий вход третьего RS-триггера, формируя информацию на выходе QD. По переднему фронту первого стробирующего импульса второй RS-триггер переключается в лог. 1 и разрешает формирование на выходе ОС тактовых импульсов положительной полярности.

На рисунке 7г показан другой вариант схемы формирователя импульсов без использования элемента «исключающее ИЛИ». При необходимости в схеме рис. 7а вместо первого RS-триггера может быть использована схема селекции признака начала кода, представленная на рисунке ба, а в схеме рис. 6а вместо схемы селекции - RSтриггер аналогично рисунку 7а.

Описание работы декодирующих устройств, построенных по схемам рис. ба и 7а, приведено для случая, когда длительность тактового интервала  $T_{\nu}$  кодирующего устройства равна длительности тактового интервала Т декодирующего устройства. При неравенстве указанных интервалов возможно смещение импульсов в точке F относительно импульсов в точке Е. Для нормального функционирования предложенных устройств необходимо, чтобы указанное смещение не превышало периода повторения импульсов задающего генератора Т/8 декодирующего устройства в течение всей информационной посылки с признаком начала кода. Следовательно, должно выполняться условие  $|T - T_{\kappa}|/T < 1/8n$ , где n суммарное количество тактовых интервалов.

При использовании восьми информационных разрядов и признака начала кода Р3 n = 11, тогда  $|T - T_{\kappa}|/T <$ < 1/88 > 1%. Выполнение указанного условия не вызывает затруднений при использовании кварцевых задающих генераторов. При необходимости количество информационных разрядов может быть увеличено по меньшей мере на порядок.

## Литература

- 1. Шевкопляс Б.В. Микропроцессорные структуры. Инженерные решения: Справочник. Радио и связь, 1990.

- 2. Климов В.П., Казанов И.М., Вишняков И.Л. Колирующие устройства оптических каналов. В сб. Электронная техника в автоматике. Радио и связь, 1985. Вып. 16. С. 257–264.