## Преимущества FPGA с технологией Tri-Gate

### Райан Кенни, Джефф Ватт, Altera Corporation

В данной статье исследуется влияние перехода дизайна транзисторов в полупроводниковой промышленности от традиционной планарной к 3D-структуре, что обеспечивает значительный рост возможностей высокоэффективных программируемых логических схем.

### Введение

В феврале 2013 года компании Altera и Intel Corporation объявили, что следующее поколение высокоэффективных FPGA-продуктов (программируемых логических интегральных схем), выпускаемых компанией Altera, будет производиться с использованием 14-нм транзисторов с 3D Tri-Gate технологией от компании Intel. Благодаря этому компания Altera становится основным поставщиком эксклюзивных полупроводниковых технологий. Чтобы понять полезность технологии Tri-Gate для высокоэффективных FPGA, необходимо ознакомиться с основными этапами её разработки и структуры, а также с сопутствующими технологиями.

### Основные этапы разработки транзисторов

В 1947 году в исследовательском центре Bell Laboratories был представлен первый транзистор германиевой «точечно-контактной» структуры. В начале 1954 года кремний использовали, чтобы производить двухполюсные транзисторы, но только в 1960 году был построен первый кремниевый МОПтранзистор (MOSFET - полевой транзистор со структурой металл-оксидполупроводник). Самые ранние MOSFET были 2D-планарными устройствами с током, текущим по поверхности проводника под затвором. Более 50 лет базовая структура устройств MOSFET оставалась практически неизменной.

Со времён появления в 1965 году закона Мура в изготовление и оптимизацию технологии MOSFET, с целью закрепления закона в номенклатуре и циклах планирования производства полупроводниковой промышленности, было внесено немало усовершенствований и улучшений. Последние 10 лет все улучшения эффективности и производительности MOSFET происходили благодаря прорывам в областях внедрения технологий «напряжённого кремния» (который обладает растянутой кристал-

лической решёткой) и High-К технологией металлического затвора (материал с высокой диэлектрической проницаемостью или высокой диэлектрической постоянной, использующийся как диэлектрик затвора).

Потенциал технологии «опоясывающего» затвора транзистора с целью повышения продуктивности MOSFET и устранения короткоканального эффекта был описан в 1991 году в статье Дига Хисамото (Digh Hisamoto) и его коллег из научно-исследовательской лаборатории Hitachi (Hitachi Central Research Laboratory): по мере уменьшения длины канала МОП-транзистора свойства последнего начинают резко отличаться от свойств обычных длинноканальных приборов. Публикация называлась «Влияние вертикальной структуры SOI «DELTA» на планарную технологию устройства» [1]. В 1997 году Управлением перспективных исследовательских проектов (DARPA) группе разработчиков из Калифорнийского университета в Беркли был выдан грант на проектировку транзистора со сверхтонким подзатворным изолятором, основанного на принципе DELTA. В одной из первых статей, посвящённой описанию результатов проведённых исследований, устройству, за тонкую структуру в центре геометрии транзистора, было дано название «FinFET» [2].

### Поворотный момент в технологии изготовления транзисторов

Оптимизация и технологические исследования 3D-структур транзисторов продолжились в научно-исследовательских организациях ведущих компаний, занимающихся полупроводниковым оборудованием. Часть процессов и запатентованных разработок были опубликованы, а некоторые так и остались в стенах корпоративных лабораторий.

Инвестициями научных исследований в полупроводниковой промышленности распоряжаются согласно Меж-

дународной дорожной карте для полупроводников (International Technology Roadmap for Semiconductors - ITRS). ITRS является одним из наиболее известных международных исследовательских проектов. Спонсорами проекта выступают организации, считающиеся ведущими разработчиками и производителями полупроводникового оборудования. ITRS сосредотачивается на прогнозировании появления новых технологий в области полупроводников, которые позволят перейти к выпуску продуктов с более высокими характеристиками. Документальные заключения ITRS и рекомендации по вопросам производственных возможностей таких технологий, как «напряжённый кремний» и металлические затворы с диэлектриком High-K, а теперь и использование 3D-транзисторов, призваны подчеркнуть справедливость закона Мура. За прошедшее десятилетие исследования в области 3D-транзисторов, основанные на докладах ITRS, а также экспертизе научных статей и патентов, существенно расширились.

### Внедрение и испытания

Транзисторы с 3D-структурой попали в центр внимания промышленности и заняли своё место в истории технологии транзисторов MOSFET благодаря двум важным заявлениям, которые были сделаны в течение последних 4 лет.

Первое заявление было озвучено 4 мая 2011 года компанией Intel Corporation. В нём сообщалось о транзисторах с технологией Tri-Gate, отобранных для планирования и изготовления полупроводникового оборудования по 22-им техпроцессу. Заявлению предшествовало десятилетие исследований и разработок. При этом использовались работы господина Хисамото (Hisamoto) и других исследователей в сфере развития и оптимизации FinFET. Оно подтверждало целесообразность и рентабельность транзисторов с технологией Tri-Gate в производстве полупроводников, а также декларировало лидерство компании Intel в полупроводниковой промышленности.

Второе заявление являлось публикацией технологической дорожной карты ITRS. Многие компании-произ-

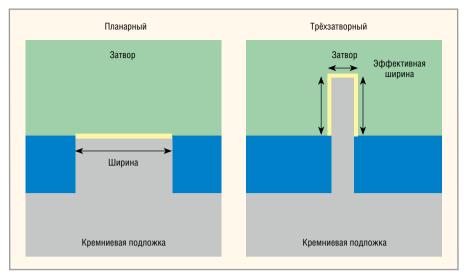

Рис. 1. Эффективность ширины каналов планарного транзистора и транзистора Tri-Gate структуры

водители полупроводникового оборудования определили технологию 3D-транзисторов как основной инструмент достижения высоких показателей в полупроводниках над техпроцессами 20-нм или 22-нм.

### Основные особенности структуры Tri-Gate

Транзисторы с 3D-геометрией иструктурой Tri-Gate имеют существенные преимущества перед транзисторами планарной структуры. Все они относятся к «опоясывающему» эффекту затворов MOSFET вокруг источника утечки. Эти преимущества отражаются в возрастающей производительности, уменьшении энергопотребления и тока утечки, компактности дизайна транзистора и в уменьшении подверженности эффекту одиночного сбоя (SEU) ионизирующими зарядами (см. рис. 1).

Ключевое преимущество транзисторов с технологией Tri-Gate перед транзисторами традиционной планарной структуры может заключаться в эффективной ширине проводящего канала.

Текущая способность проводимости и производительности транзистора непосредственно пропорциональна эффективной ширине канала. Эффективная ширина канала в транзисторе с 3D-структурой может быть значительно увеличена относительно планарного благодаря способности увеличивать ширину в третьем измерении, как показано на рисунке 1. Это улучшает приспособляемость конструкции для проектировщика транзистора и увеличивает производительность без тех ухудшений, которые появляются при увеличении ширины канала в планарном транзисторе.

Преимущество по энергопотреблению проявляется благодаря усилению контроля канала электрическим полем затвора на трёх сторонах ребра. Это понижает порог тока утечки от истока до стока в «закрытом» состоянии по сравнению с планарным транзистором. Кроме того, благодаря Tri-Gate транзисторам, мощность напряжения может быть значительно уменьшена, и в то же время из-за увеличенной эффективной ширины канала, по сравнению с планарным транзистором, будет поддерживаться большая скорость. В результате эффективный расход энергии и уменьшение тока утечки дают существенную экономию энергии.

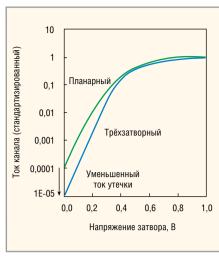

Преимущество в энергосбережении на своих форумах Intel Developer Forums (2011, 2012) компания Intel Corporation объясняла более крутой подпороговой кривой Tri-Gate транзистора (см. рис. 2). Проектировщики также могут использовать преимущества более крутой подпороговой кривой для сокращения тока утечки планарного транзистора той же производительности и для транзистора существенно более высокой производительности, а также для комбинации обоих.

При появлении каждого нового поколения технологии производства кремния происходит сжатие геометрии транзистора или уменьшение общей его структуры и затвора, что увеличивает плотность. Сама 3D-структура Tri-Gate также приводит к увеличению плотности транзисторов, увеличивая ширину проводящего канала транзистора в третьем измерении. Это позволяет проектировщикам выбирать альтернативный размер и шири-

Рис. 2. Транзисторы структуры Tri-Gate с более крутой подпороговой кривой

ну «ребра», основываясь на рабочих характеристиках, производительности и плотности транзистора. В случае если Altera перейдёт на структуру Tri-Gate по 14-нм техпроцессу, компания извлечёт из этого немалую выгоду: сжатие геометрии транзистора до 14-нм техпроцесса и дальнейшее увеличение плотности благодаря технологии Tri-Gate в 3D-транзисторах.

Снижение влияния эффекта одиночного сбоя (SEU) достигается благодаря небольшой площади поперечного сечения соединения ребра с основанием в структуре Tri-Gate. Это уменьшает область, в которой может быть коллектирован заряд, произведённый ионизацией частицы, что наблюдается в транзисторах плоскостной структуры. Малая вероятность появления заряженных частиц, вызывающих всплески в схемах, основанных на транзисторах, подтверждается ранними тестированиями внедрения транзисторов Tri-Gate в устройства Intel по 22-нм техпроцессу.

### Производство устройств на основе технологии Tri-Gate

Преимущества транзисторов Tri-Gate изучены и достаточно хорошо известны, но при внедрении их в устройства ориентируются не только на технологии и возможности производства, но, в первую очередь, на рентабельность.

Производство полупроводников малых конфигураций (40-нм, 28-нм, 22-нм или 20-нм и выше) требует больших расходов на научные исследования. Именно это ограничивает применение данной технологии, так как на её развитие требуются миллиарды дол-

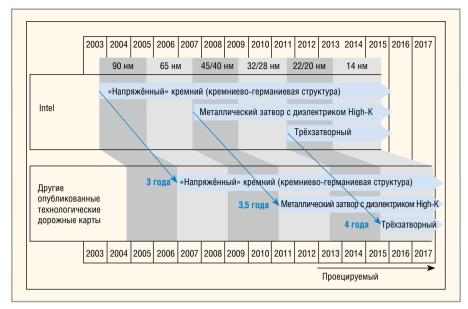

Рис. 3. Лидерство Intel в транзисторных технологиях

ларов. В результате извлечь выгоду из транзисторов с 3D-технологией способна только группа компаний. Intel Corporation – единственная компания, которая уже осуществила проектирование по 22-нм техпроцессу и может предоставить готовые данные для массового производства транзисторов с технологией Tri-Gate. Так в первом квартале 2013 года компанией было выпущено 100 млн единиц продукции, основанных на технологии Tri-Gate.

Был выявлен ряд проблем и некоторых особенностей затворов 3D-структуры, что повлекло за собой подгонку производства и самой структуры транзисторов под имеющиеся технологии. Речь идёт о моделировании новых паразитных ёмкостей, чего не делалось в традиционных планарных структурах, а также о пересмотре планировки и использовании методов двойной литографии на имеющемся оборудовании для формирования более частых рёбер.

Автоматизация процесса проектирования электроники (EDA) также является важным фактором, влияющим на удобство использования разработчиком FinFET и Tri-Gate технологий. В 2013 году обучением проектированию полупроводниковых продуктов будущего с учётом влияния правил применения Tri-Gate занимались в основном две компании – Cadence и Synopsys.

# Влияние на **FPGA**и на производительность других полупроводниковых устройств

Главное преимущество технологии Tri-Gate для электронных устройств, основанных на FPGA, подтверждает закон Мура и заключается в устойчивом развитии улучшений в плане плотности, эффективности, энергопотреблении и стоимости транзистора. Это касается индустрии бытовой электроники, развития компьютерного оборудования, усложнения ПО, устройства хранения памяти, разработки и креативности мобильных устройств, а также автоматизации и производительности управленческих работ.

Благодаря этой технологии значительно улучшился контроль над рассеиванием мощности в полупроводниках как в статическом, так и в активном состоянии. Благодаря этому программируемая логика, подкреплённая 14-нм техпроцессом, способна конкурировать с ASIC (специализированными интегральными микросхемами) и ASSP (специализированными стандартными продуктами - разновидностью специализированных интегральных схем). Она даёт значительные преимущества при программировании, влияет на производительность, добавляет универсальности, позволяет использовать Open Computing Language (OpenCL™ - открытый язык вычислений) проектирования программного обеспечения и интеграцию DSP (технологии управления и оптимизации), трансиверы и конфигурируемые I/Os.

В своём отчёте перед инвесторами компания Intel Corporation предоставила данные обо всех тех преимуществах, которые были выявлены в процессе внедрения технологии Tri-Gate

в микропроцессорные устройства компании. Это сокращение потребляемой транзистором мощности более чем на 50% при переходе от планарной структуры по 32-нм техпроцессу к Tri-Gate структуре по 22-нм техпроцессу [3], улучшенная кривая плотности распределения ошибок [3] и снижение степени подверженности SEU в 4–10 раз [4].

### Место компании Intel в полупроводниковых технологиях

На нескольких общественных форумах, включая Intel Developer's Forums, и на конференциях инвесторов Intel определила те области, в которых компания будет сохранять лидерство. На рисунке 3 показаны расчёты компании Intel, определяющие количество лет, в течение которых она будет оставаться лидером в своей отрасли благодаря своевременному внедрению технологии «напряжённого кремния» и технологии металлического затвора High-K в серийное производство. Учитывая производственное развёртывание технологии Tri-Gate по 22-нм техпроцессу в 2011 году, Intel оценивает свой отрыв от конкурентов сроком в четыре года.

«В первом квартале 2013 года мы уже отгрузили 100 млн 22-миллимикронных (Tri-Gate) процессоров, используя нашу революционную транзисторную 3D-технологию, в то время как другие всё ещё работают над созданием своих первых блоков», – сказал в ходе телеконференции, проходившей 16 апреля 2013 года и посвящённой финансовой деятельности компании, генеральный директор Intel Пол Отеллини (Paul Otellini).

Другое ключевое преимущество, которое поможет Intel внедрить технологии по 14-нм техпроцессу, - это их знаменитая стратегия «Tick-Tock». Цикл «Tick» подразумевает внесение изменений в микроархитектуру СРUпродуктов. Далее следует цикл «Tock» уменьшение геометрии полупроводника. Intel намерена продолжить сжатие геометрии транзисторов с 22 нм до 14 нм. Что касается аналогичных технологических процессов на полупроводниках у других изготовителей, то пока неизвестно, предусматривают ли их дорожные карты дальнейшее сжатие.

## Доступ к преимуществам технологии Tri-Gate через FPGA Altera

Воспользоваться преимуществами технологии Tri-Gate компании Intel смогут только пользователи высокоэффективных FPGA, выпущенных компанией Altera® по 14-нм техпроцессу. Это результат особого производственного сотрудничества двух компаний, упомянутых в начале статьи.

Существенные преимущества полупроводниковой технологии Tri-Gate позволят компании Altera наделять SoC и FPGA невероятной производительностью. Объём работы ядра, по сравнению с другим FPGA высокого уровня, удвоится, что выведет продуктивность работы FPGA на уровень гигагерца. При этом энергопотребление, благодаря комбинации процесса, архитектуры и усовершенствования программного обеспечения, уменьшится на 70%.

Несмотря на то что детали производственного 14-нм процесса от Intel Corporation ещё не обнародованы, пользователи Altera могут уже сегодня воспользоваться преимуществами, которые дают FPGA-устройствам технологии Tri-Gate: производительностью и малым энергопотреблением. Это возможно благодаря линейке продуктов Arria® 10 для FPGA. Затем пользователи смогут воспользоваться дизайном Pin-for-Pin, перейдя со временем с Arria 10 FPGA и SoC на Stratix® 10 FPGA и SoC.

Это позволит пользователю FPGA и разработчику архитектуры системы начать проектировать продукты, которые смогут сочетать в себе программы

Аггіа 10 и Stratix 10, притом с минимумом изменений, модификаций и реконструирования. В результате выпускаемые FPGA будут обладать самой высокой производительностью и самым низким уровнем энергопотребления среди аналогов, созданных по 20-нм процессу, что сопоставимо с производительностью и энергопотреблением этих же продуктов, созданных по технологии Intel 14 нм с использованием Tri-Gate.

### Заключение

Исторически сложилось так, что определение самых высокоэффективных продуктов FPGA - это весьма субъективный параметрический процесс сравнительного анализа. Но использование технологии Tri-Gate по 14-им техпроцессу создаст самые высокоэффективные FPGA, которые, безусловно, превзойдут транзисторные технологии. Технология Intel Tri-Gate по 14-нм техпроцессу станет уже вторым поколением высокопродуктивной технологии. Intel Tri-Gate по 14-нм техпроцессу сочетает в себе как выгоды технологии Tri-Gate, так и преимущества сокращения полного транзисторного процесса. Единственная компания, имеющая доступ к данной технологии Intel, - это Altera. Проектирование систем с использованием технологии, основывающейся на Tri-Gate, - гарантия целого ряда преимуществ.

### Литература

1. Impact of the Vertical SOI «DELTA» Structure on Planar Device Technology,

- IEEE Transactions on Electron Devices. Vol. 38. No. 6. June 1991. www.ieeexplore. ieee.org/iel1/16/2677/00081634.pdf.

- FinFET A Self-Aligned Double-Gate MOSFET Scalable to 20 nm, IEEE Transactions on Electron Devices. Vol. 47. No. 12. December 2000. www.eecs.berkeley.edu/~hu/PUBLI-CATIONS/PAPERS/700.pdf.

- 3. *Mark Bohr*. Intel Developer's Forum. 6 September 2011. www.intel.com/idf/library/pdf/sf\_2011/SF11\_SPCS002\_101F.pdf.

- Soft Error Susceptibilities of 22 nm Tri-Gate Devices, IEEE TRANSACTIONS ON NUCLEAR SCIENCE. Vol. 59. No. 6. December 2012. www.ieeexplore.ieee.org/iel5/23/ 4689328/06338321.pdf.

- Intel Adds Altera as a Customer. The Wall Street Journal. 25 February 2013. www.online.wsj.com/article/SB1000142412 7887323384604578326641821604714.html.

- Intel Reinvents Transistors Using New 3D-Structure. Intel Corporation. 4 May 2011. www.newsroom.intel.com/community/ intel\_newsroom/blog/2011/05/04/intelreinvents-transistors-using-new-3-dstructure.

- International Technology Roadmap for Semiconductors. ITRS.com. 2011. www.itrs.net/.

- 8. Intel Earnings Call 1Q2013. 16 April 2013. www.newsroom.intel.com/community/intel\_newsroom/blog/2013/04/16/intelreports-first-quarter-revenue-of-126-billion.

- White Paper: Meeting the Performance and Power Imperative of the Zettabyte Era with Generation 10 FPGAs and SoCs. Altera.com. June 2013. www.altera.com/literature/ wp/wp-01200-power-performance-zettabytegeneration-10.pdf.

Перевод Эрмина Машуряна

### Новости мира News of the World Новости мира

## **Японская революция** в микроэлектронике

Японская компания MinimalFab продемонстрировала на выставке Semicon Japan 2014 линию, переворачивающую наши представления о производстве чипов.

Вместо огромных чистых комнат и оборудования мегаразмеров предлагаются минифабы для производства отдельных чипов размером полдюйма.

Компания (как стартап) была организована четыре года назад. Прямо на выставке была за два дня безо всяких чистых комнат развернута линия из 25 отдельных установок и в течение дня представлен полный цикл создания К-МОП транзисторной

структуры. Линия включает в себя все стандартные процессы: от нанесения фоторезистов (через фотолитографию и ионную имплантацию) до контроля функционирования. Кристаллы помещены в специальные вакуумноизолированные мини-контейнеры, что в итоге не требует специальных чистых комнат.

На данный момент технология освоена под 0,8 мкм. Ожидается, что через два года удастся отработать 22 нм.

Небольшая производительность, мультитехнологичность, минимальная стоимость чипа (ориентировочная стоимость всего комплекта оборудования из 55 установок составляет приблизительно

\$ 5 млн), отсутствие чистых комнат и громадных затрат, с этим связанных, — именно то, что нужно российскому рынку сегодня, да и завтра!

www.zelenograd.ru